Cortex M4 Vector Table

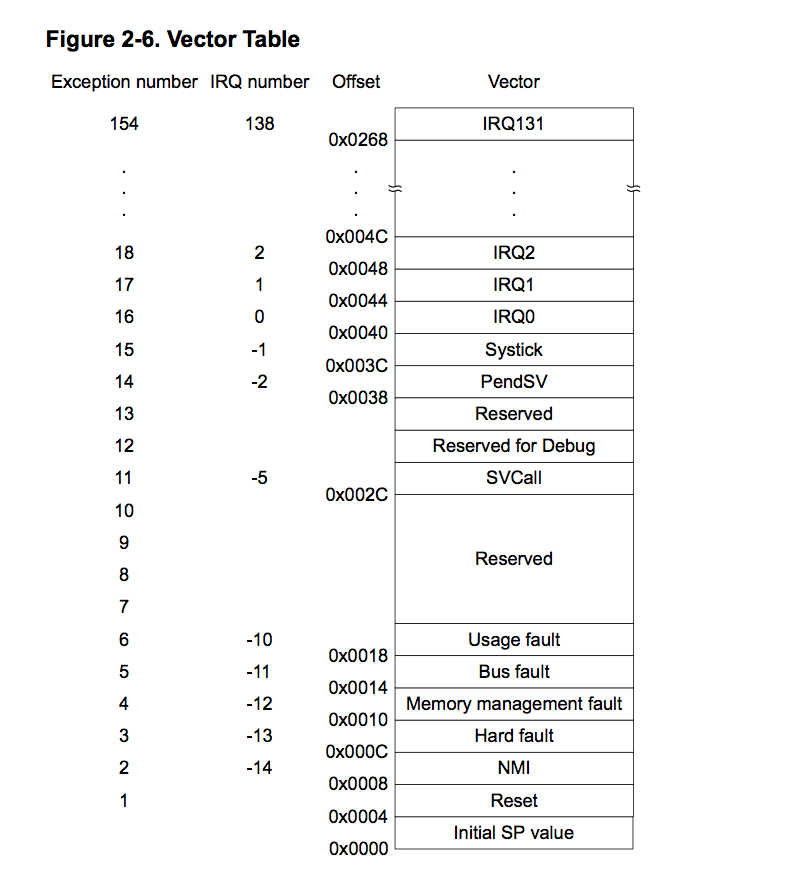

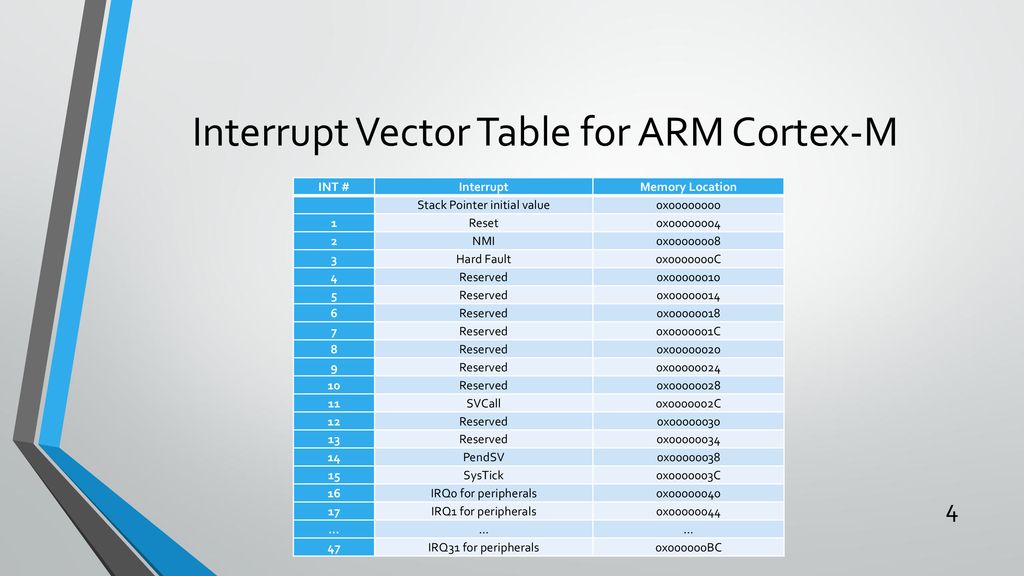

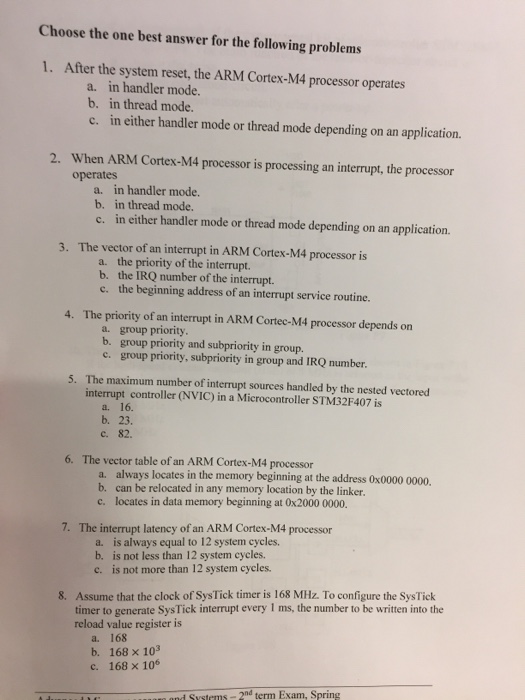

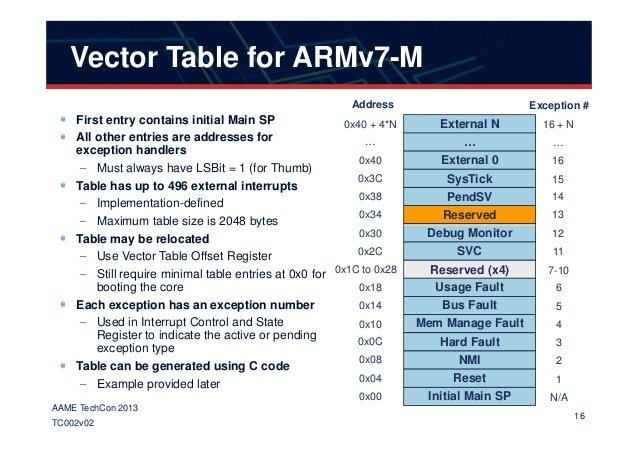

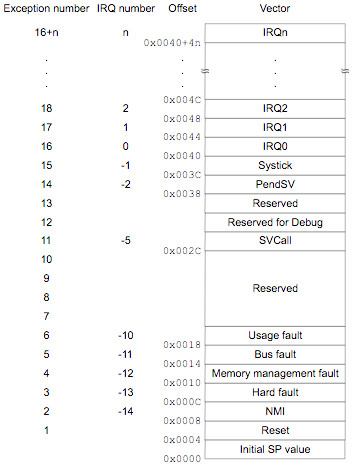

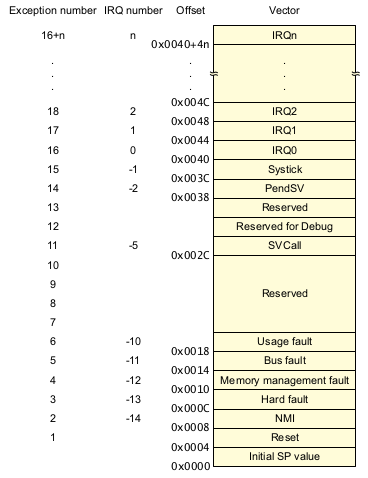

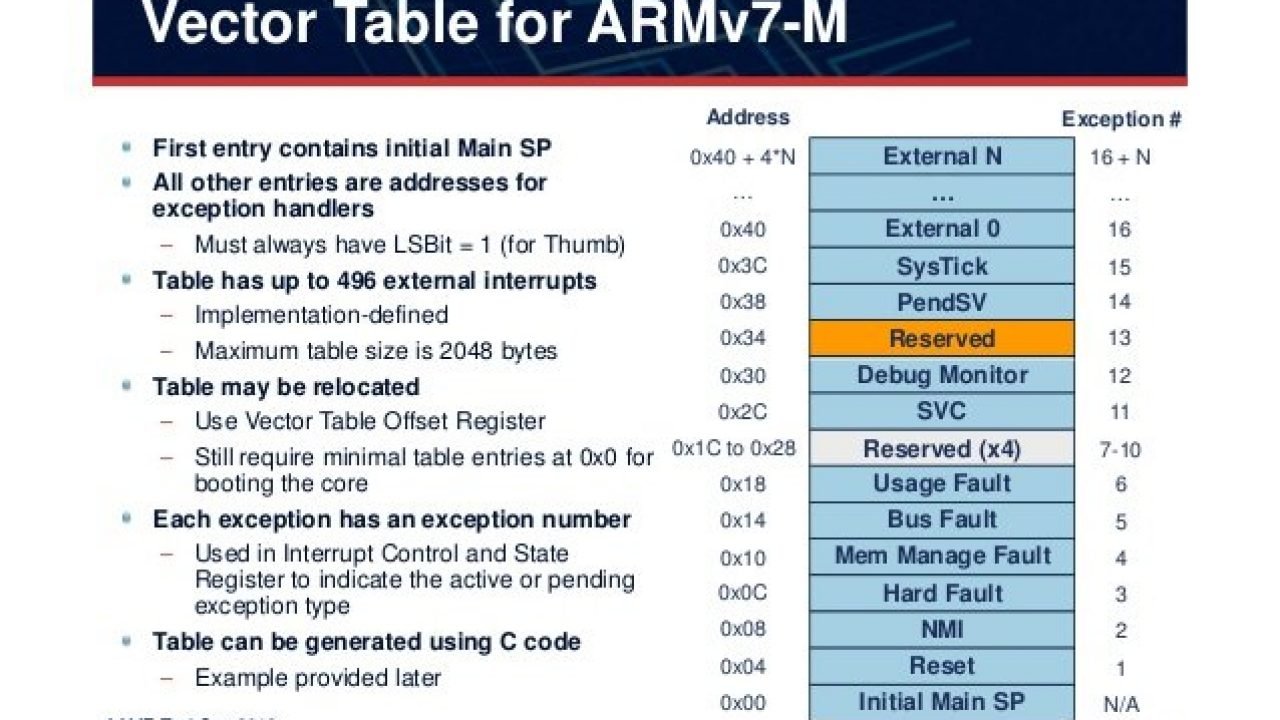

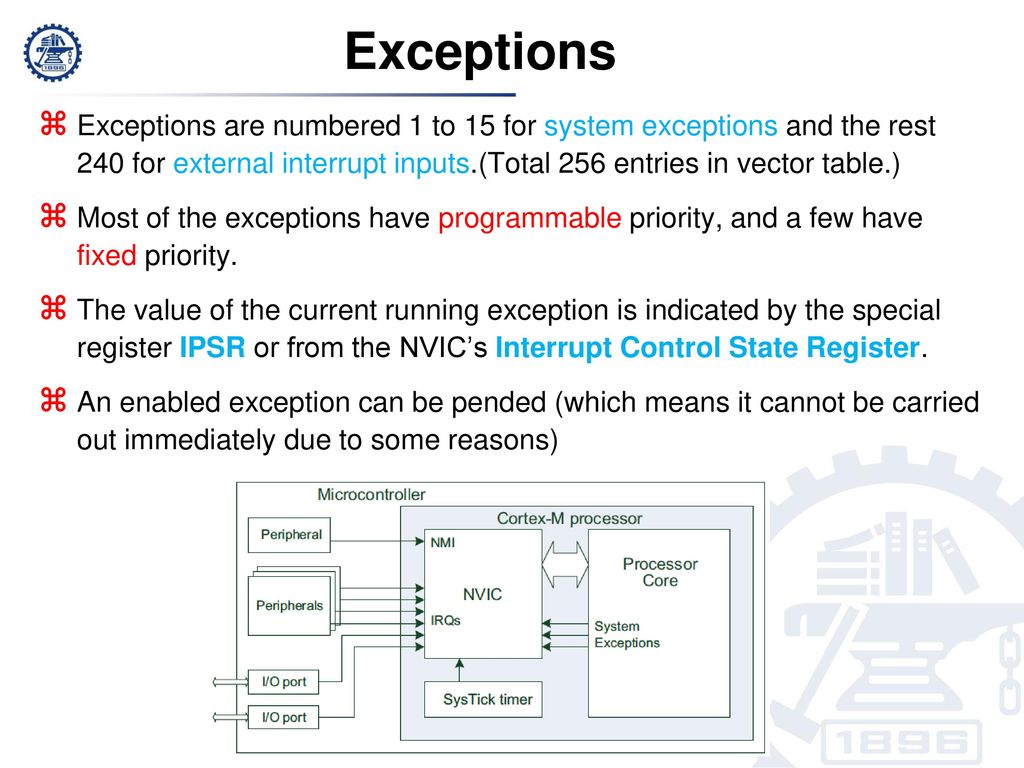

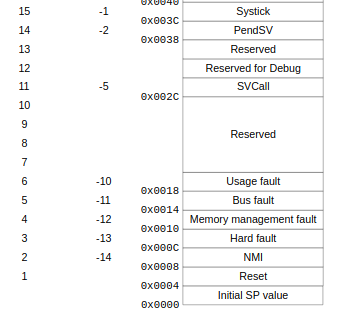

Furthermore, each interrupt/exception also has a unique interrupt number assigned to it.

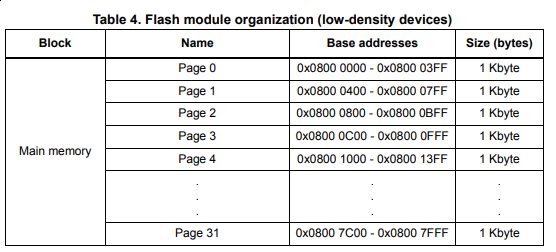

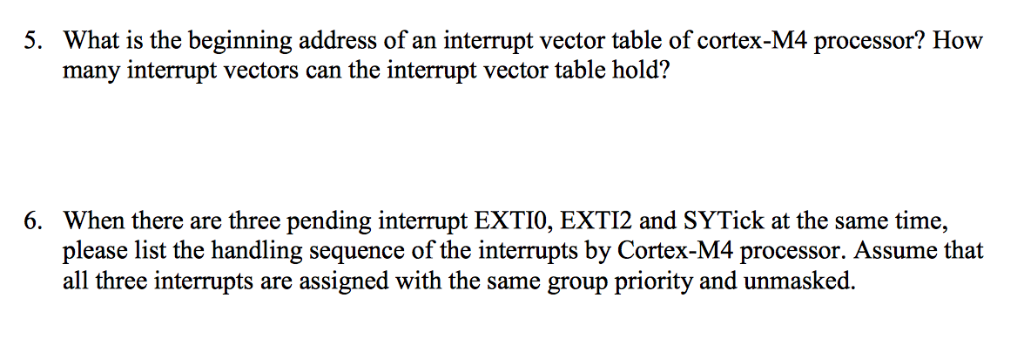

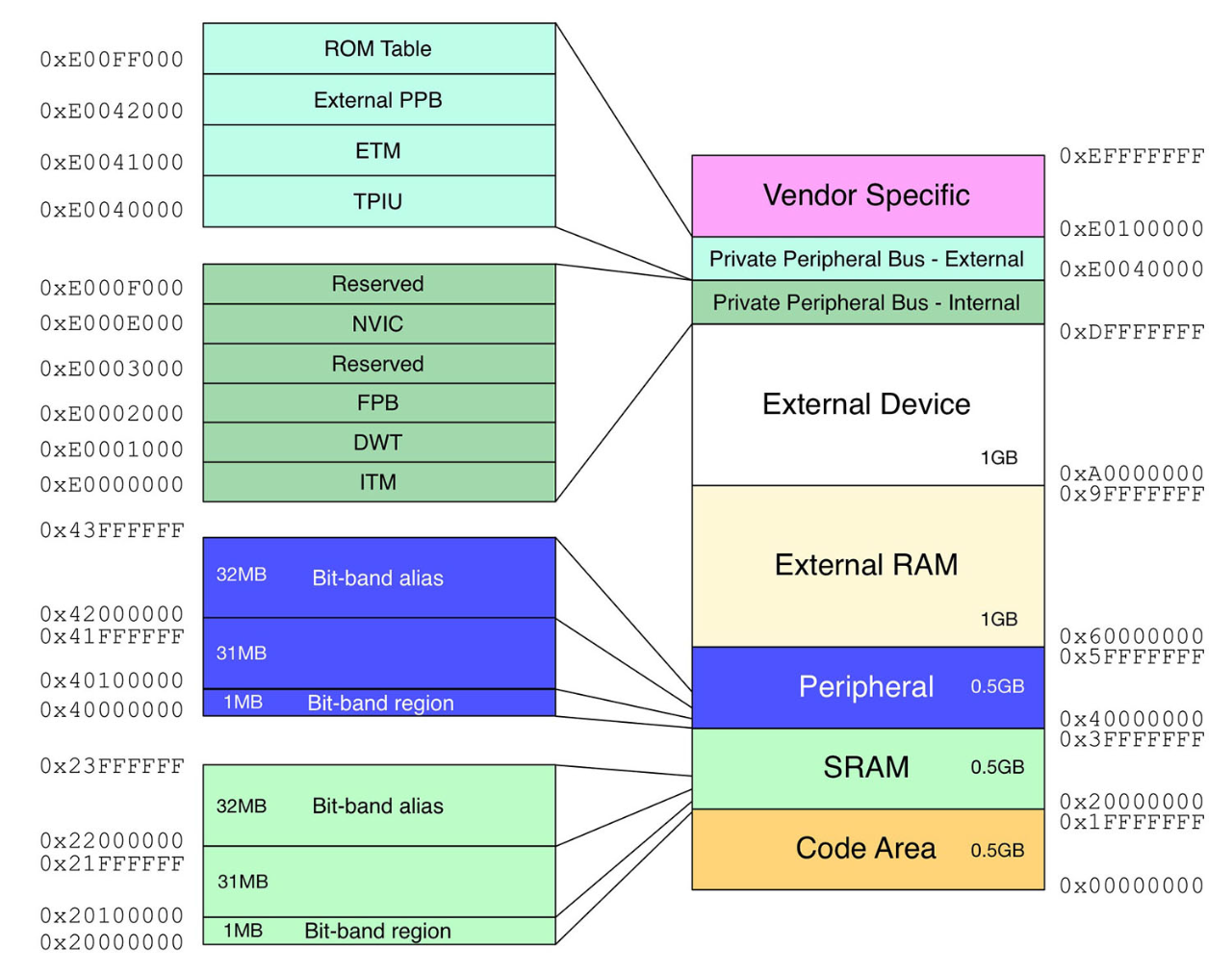

Cortex m4 vector table. As you can see, the interrupt vector table is an array of memory addresses. The interrupt vector table has eight entries. The ARM Cortex-M is a group of 32-bit RISC ARM processor cores licensed by Arm Holdings.These cores are optimized for low-cost and energy-efficient microcontrollers, which have been embedded in tens of billions of consumer devices.

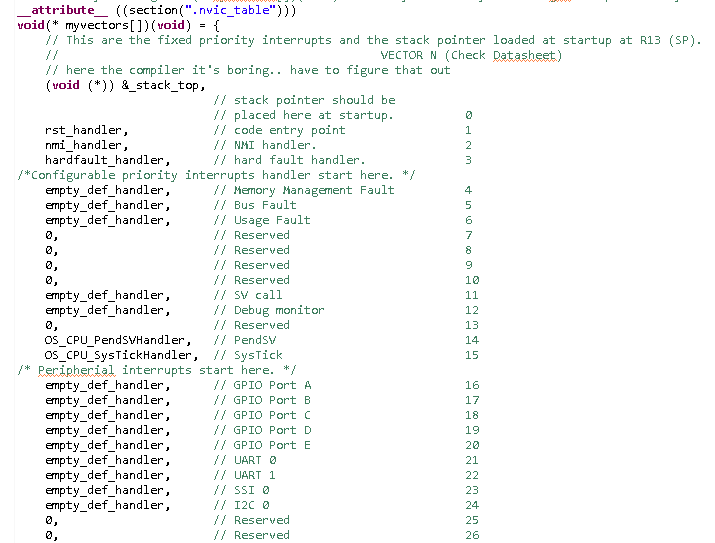

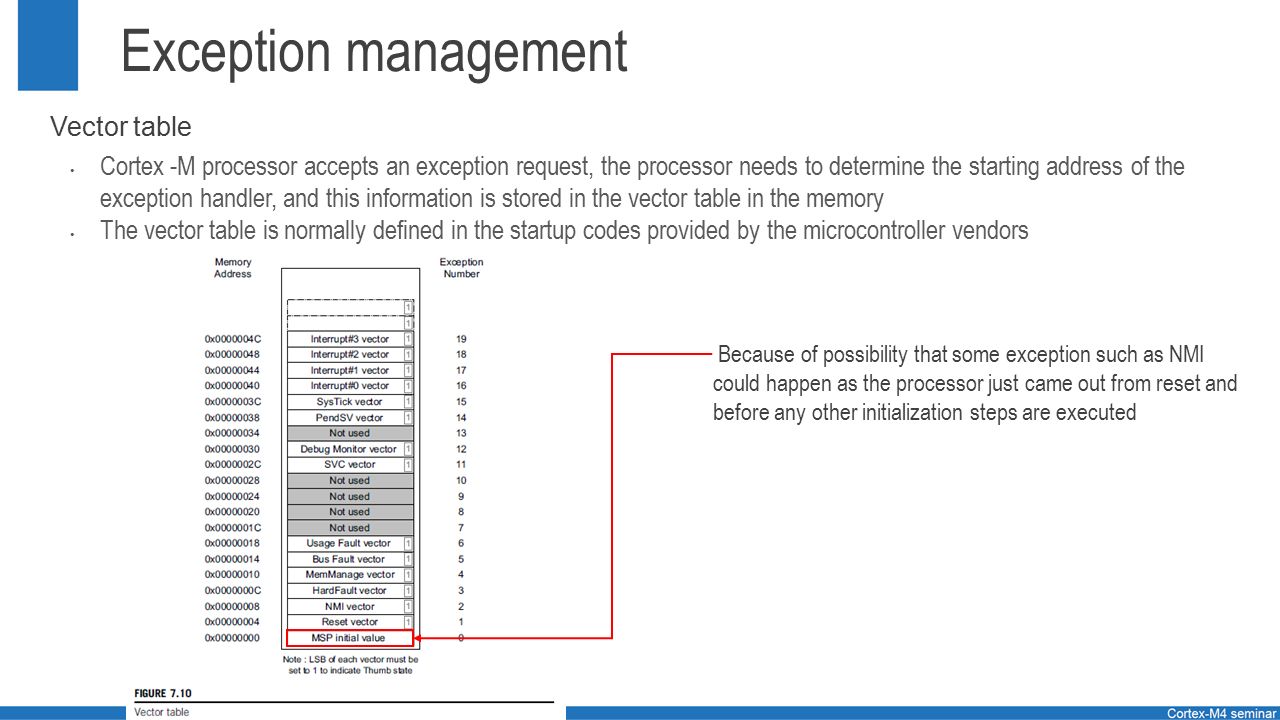

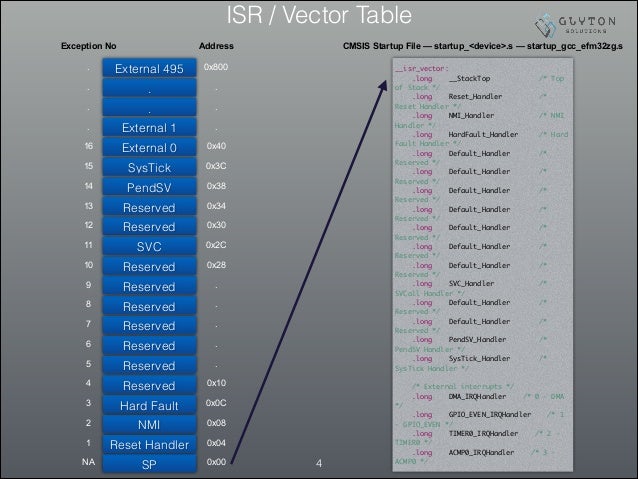

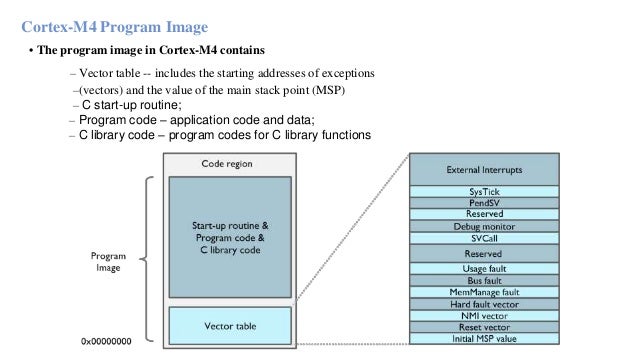

– C start-up routine;. The vector table in ARM Cortex M series looks like:. As we have discussed in the last section, the vector table contains the address of the ISR routines of all interrupts and exceptions that the microcontroller supports.

Cortex M Vector Table. Each vector has 4 bytes, containing a branching instruction in one of the following forms:. Peripheral interrupts are also defined as simple exceptions in literature.

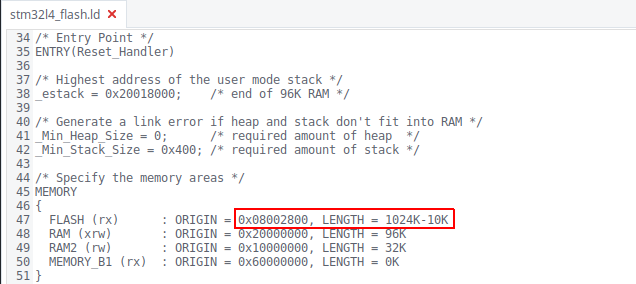

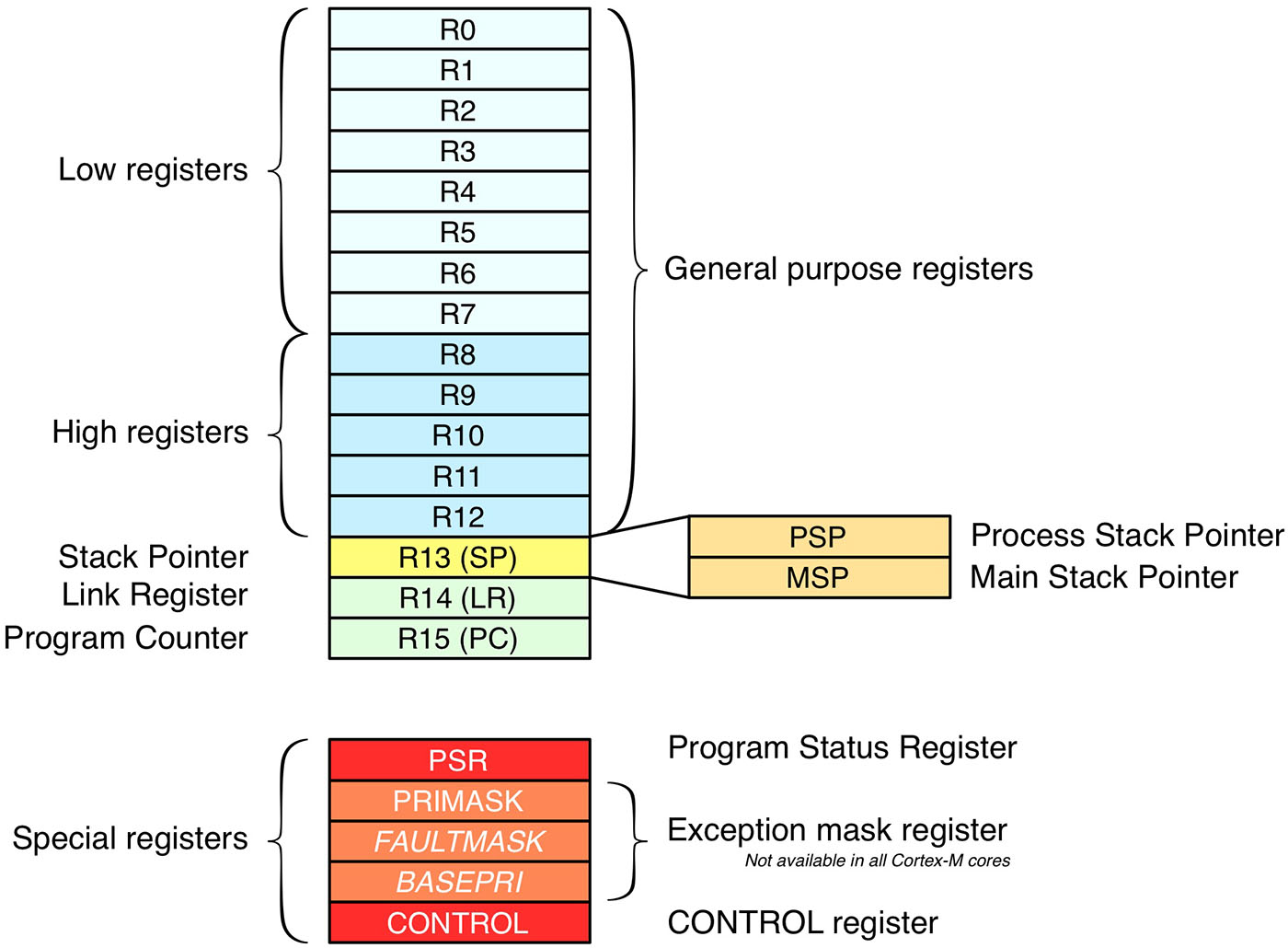

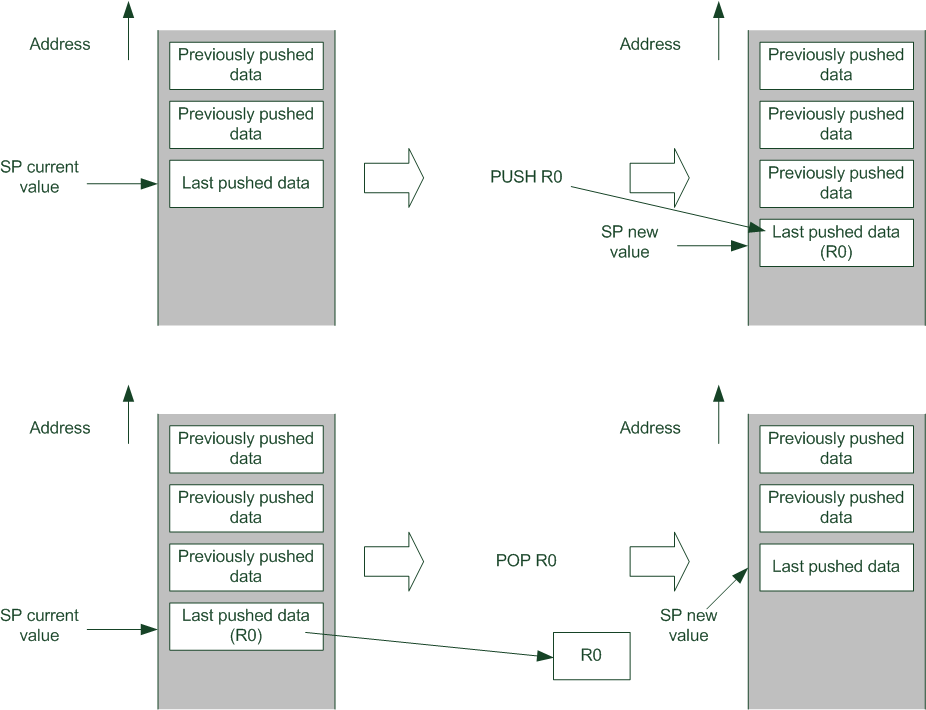

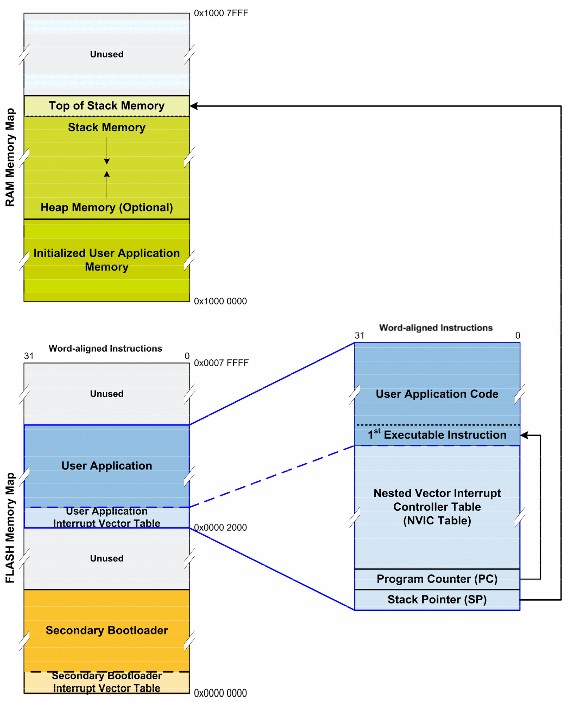

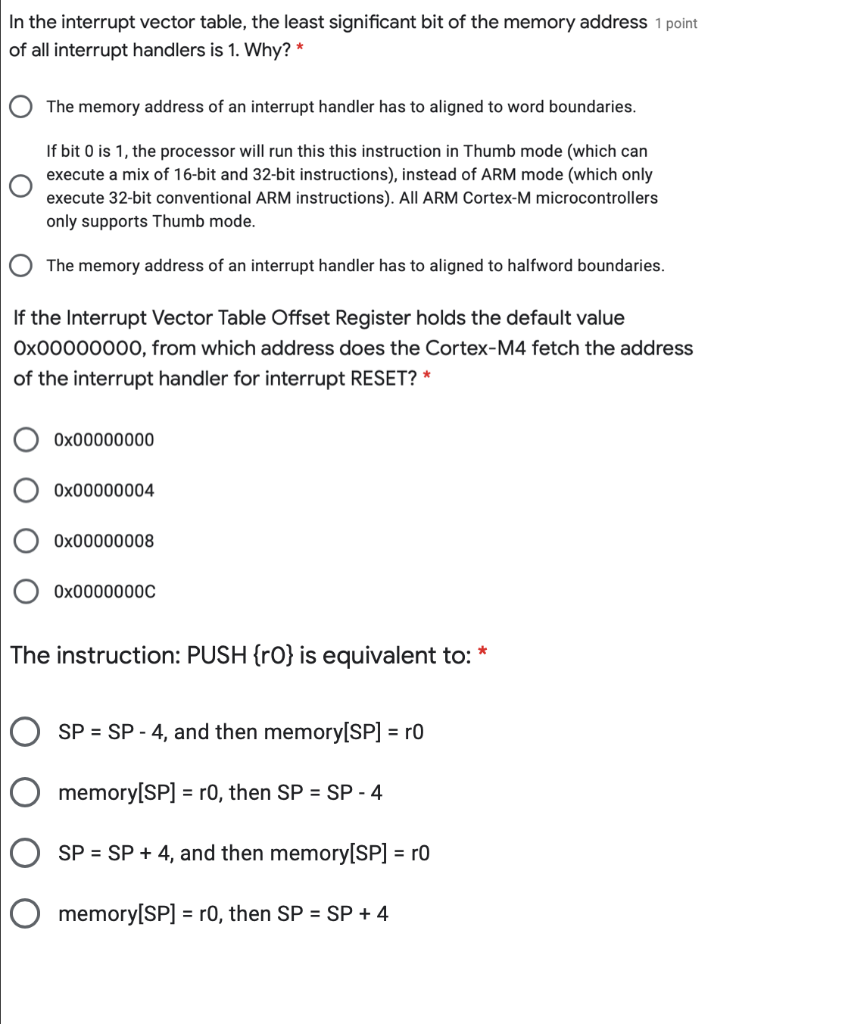

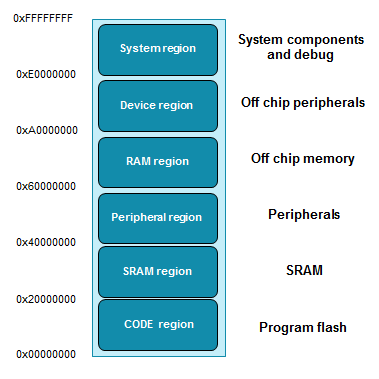

Upon encountering a B instruction, the ARM processor will jump immediately to the address given by adr, and will resume execution from there.The adr in the branch instruction is an offset from the current value of the program counter (PC) register. The Cortex ® -M4 with FPU CPU always fetches the reset vector on the ICode bus. The ARM core, up on boot up, loads the stack pointer with the value stored at offset 0.

– Program code – application code and data;. This would explain why this bit has to be set accordingly, telling the core to use the system bus and access the SRAM. Maybe on an interrupt the ICode bus is used, which cannot access the SRAM even when remapped (I don't know if this is true).

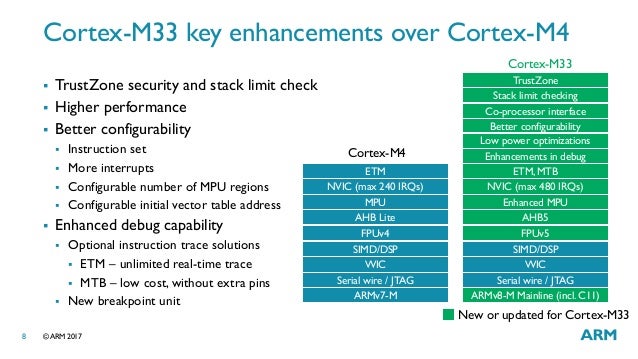

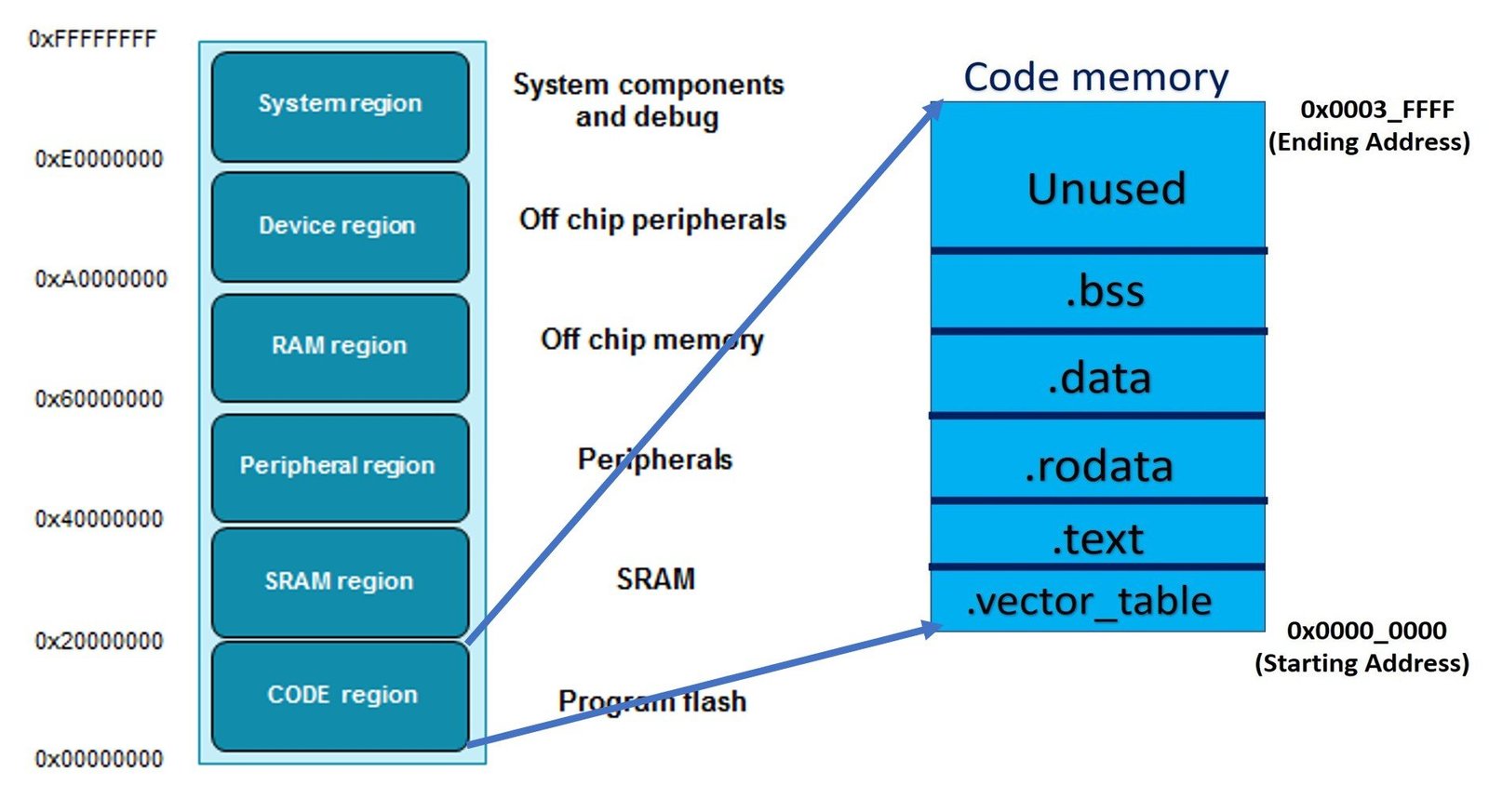

Cortex-M4 Program Image ECE 5655/4655 Real-Time DSP 3–11 Cortex-M4 Program Image † The program image in Cortex-M4 contains – Vector table -- includes the starting addresses of exceptions (vectors) and the value of the main stack point (MSP);. The cores consist of the Cortex-M0, Cortex-M0+, Cortex-M1, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23, Cortex-M33, Cortex-M35P, Cortex-M55. It contains the starting address of all exception handlers.

If you check the datasheet of TM4C123G ARM Cortex M4 microcontroller, it has 15 system exceptions and 138 peripheral interrupts. Typically, on power-on reset, the Vector table base address is defined to be at 0. And then it loads the Program counter with the address available at offset 4 and starts executing.

The figure below shows the interrupt vector table of the ARM Cortex-M4 microcontroller.

Arm Cortex M3 Boot Process Programmer Sought

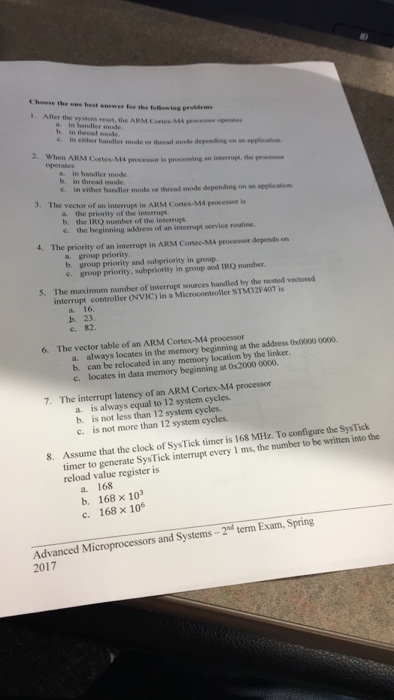

Solved After The System Reset In Arm When Arm Certex M4 Chegg Com

Cortex M3 Devices Generic User Guide

Cortex M4 Vector Table のギャラリー

Software Development In Ar Mv8 M Architecture Yiu

Embedded Gadgets Lab Initialization Of Armv8 M Trustzone Secure

Arm Cortex M Wikipedia

07 Startup Code Vector Table Nclabmd

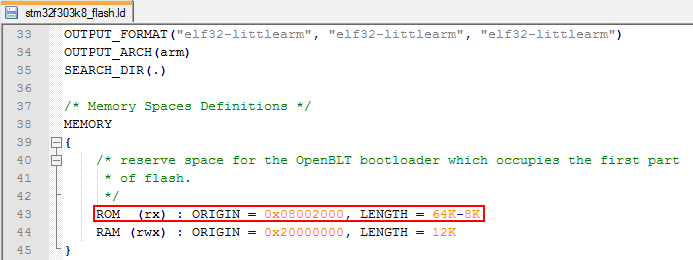

Manual Ports Armcm4 Stm32 Openblt Bootloader

Understand The Gnu Assembler Startup File Of Cortex M4

Multiple Cortex M Processing Cores Valpont

Analyzing Arm Cortex Based Mcu Firmwares Using Binary Ninja Kudelski Security Research

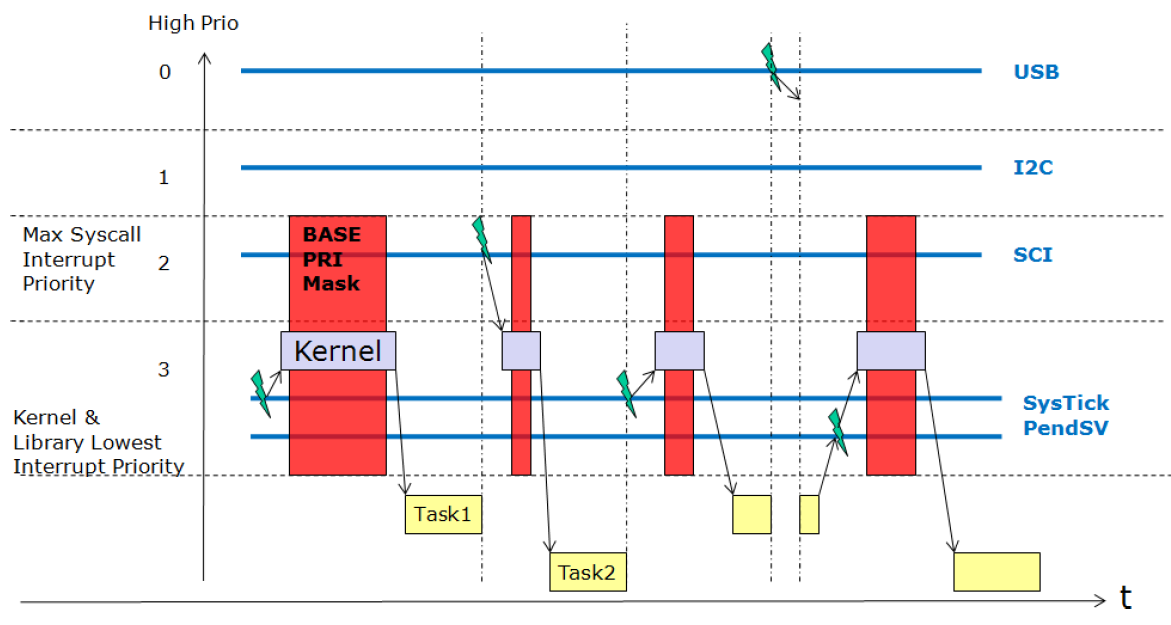

Arm Cortex M Interrupts And Freertos Part 3 Mcu On Eclipse

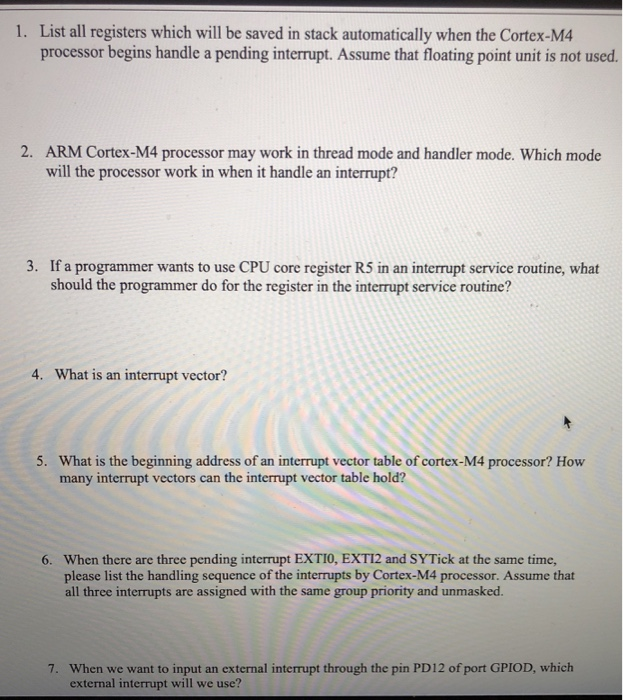

5 What Is The Beginning Address Of An Interrupt V Chegg Com

How To Debug A Hardfault On An Arm Cortex M Mcu Interrupt

Beginner Guide On Interrupt Latency And Arm Cortex M Processors Processors Blog Processors Arm Community

07 Startup Code Vector Table Nclabmd

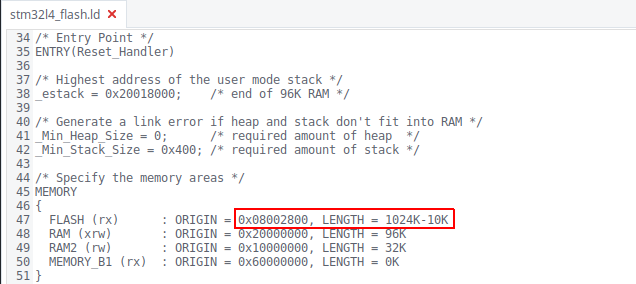

Manual Ports Armcm4 Stm32l4 Openblt Bootloader

6 2il Kvfjj Fm

Reverse Engineering Of Arm Microcontrollers Rado Rc1 Security Hardware Reversing

Interrupt And Exception Programming Ppt Download

Interrupt Vector Table An Overview Sciencedirect Topics

Cortex M3 Devices Generic User Guide

Cmsis Core Device Templates

Cortex M0 Boot Castells

Interrupt Vector Table An Overview Sciencedirect Topics

Arm Cortex M Interrupts And Freertos Part 1 Mcu On Eclipse

펌 Stm32 Memory Map 네이버 블로그

Arm Cortex M Interrupts And Freertos Part 3 Dzone Iot

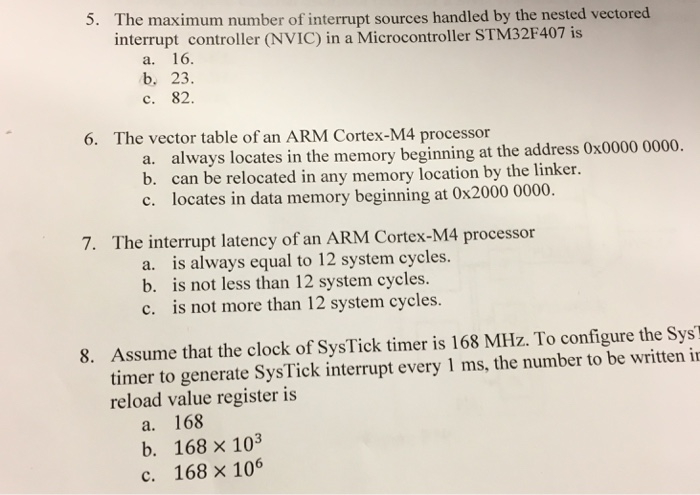

Solved The Maximum Number Of Interrupt Sources Handled By Chegg Com

Porting Ucosiii On Cortex M4 Lm4f1xl Other Microcontrollers Forum Other Microcontrollers Ti E2e Support Forums

Exception Vector An Overview Sciencedirect Topics

Arm Cortex M Interrupts And Freertos Part 1 Dzone Iot

Exceptions And Interrupts Chap 7 8 Tae Min Hwang Ppt Download

Reset Vector An Overview Sciencedirect Topics

A Practical Guide To Arm Cortex M Exception Handling Interrupt

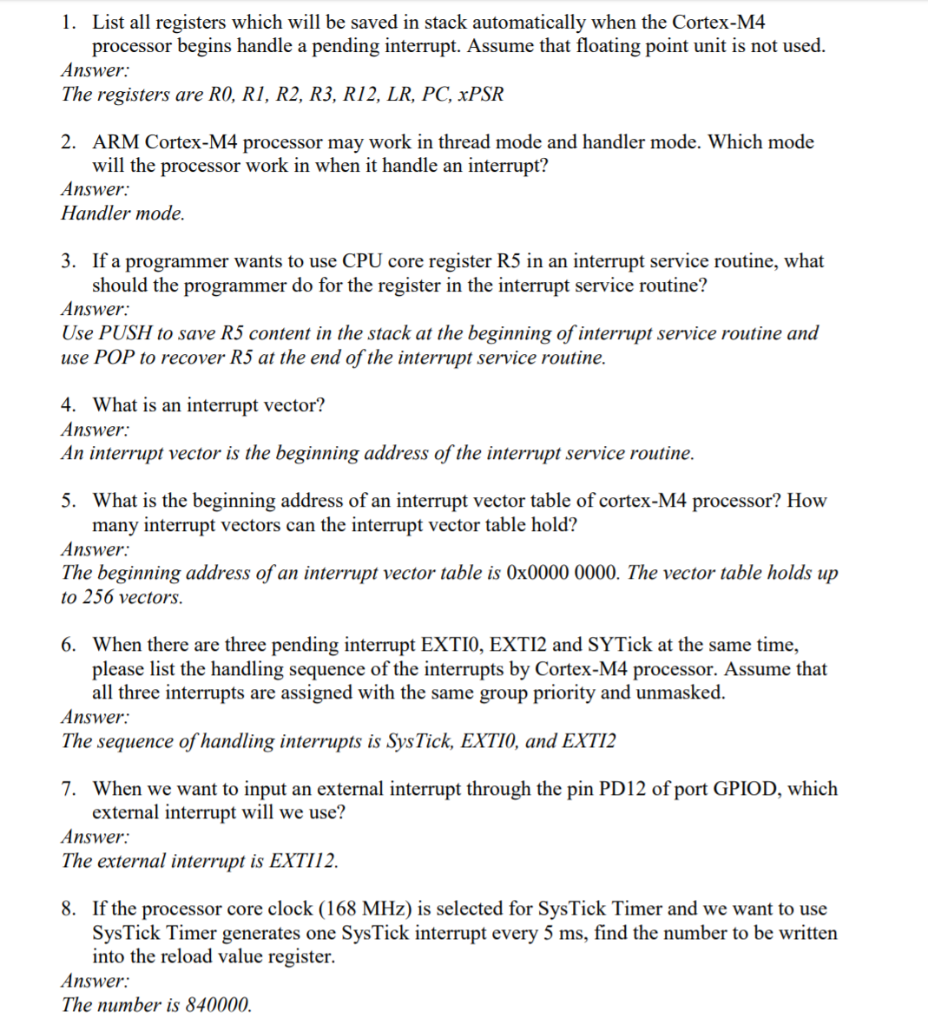

1 List All Registers Which Will Be Saved In Stack Chegg Com

펌 Stm32 Memory Map 네이버 블로그

Arm Cortex M Interrupts And Freertos Part 1 Dzone Iot

Interrupt Vector Address In Program Counter Electrical Engineering Stack Exchange

A Practical Guide To Arm Cortex M Exception Handling Interrupt

Solved After The System Reset The Arm Cortex M4 Processo Chegg Com

Reset Vector An Overview Sciencedirect Topics

Debugging Hard Faults On Arm Cortex M Mcu On Eclipse

What Is Interrupt Vector Table In Arm Cortex M Microcontrollers

Arm Cortex M Wikipedia

How Much Stack Memory Do Cortex M Applications Need Processors Blog Processors Arm Community

Lecture 9 Interrupts Youtube

Interrupts In The Ar M V7 M Are Handled By The Nes Chegg Com

Cortex M4 Technical Reference Manual

Interrupt Vector Table An Overview Sciencedirect Topics

A Practical Guide To Arm Cortex M Exception Handling Interrupt

Arm How To Write A Bootloader

Community Arm Com Cfs File Key Communityserver Blogs Components Weblogfiles 00 00 00 37 85 Cortex 2d00 M For Beginners 2d00 17 5f00 En 5f00 V2 Pdf

A Practical Guide To Arm Cortex M Exception Handling Interrupt

Arm Explains Good Interrupt Control For Low Power Processors

What Is Nested Vector Interrupt Control Nvic

Interrupt Handling In Arm Cortex M Embien Technology Blog

A Practical Guide To Arm Cortex M Exception Handling Interrupt

00xnor Sergey Ostrikov Cortex M4 Core Registers

Arm Cortex M Interrupts And Freertos Part 1 Dzone Iot

Manual Ports Armcm4 Stm32f3 Openblt Bootloader

32 Bit Xmc Industrial Microcontroller Based On Arm Cortex M Infineon Technologies

Arm Cortex M Interrupts And Freertos Part 3 Dzone Iot

Arm Cortex M3 Boot Process Programmer Sought

Primary And Secondary Bootloaders For Cortex M Processors Valpont

Manual Ports Armcm4 Tm4c Openblt Bootloader

Reset Sequence In Arm Cortex M4 Embetronicx

Arm Cortex M Bootup Cmsis Part 2 3

Http Ccrs Hanyang Ac Kr Webpage Limdj Embedded Cortex M Pdf

A Deeper Look At The Stm32f4 Project Template Getting Things Started Charles Korn

Handler Mode An Overview Sciencedirect Topics

Arm Cortex M Interrupts And Freertos Part 1 Dzone Iot

Errors In Definitive Guide For Arm Cortex M Books Processors Blog Processors Arm Community

Exception Vector An Overview Sciencedirect Topics

Solved In The Interrupt Vector Table The Least Significa Chegg Com

Exception Vector An Overview Sciencedirect Topics

Http Wiki Csie Ncku Edu Tw Embedded 15q1w4 Interrupt Part2 Pdf

Arm Cortex M Rtos Context Switching Interrupt

Cortex M0 Vector Table Avr Freaks

Solved If The Interrupt Vector Table Offset Register Hold Chegg Com

Arm Cortex M4 Programmer Model

Context Switching In Arm Cortex M3 M4 Wisesciencewise

Exception Vector An Overview Sciencedirect Topics

Tock Embedded Operating System Walkthrough

Www Eng Auburn Edu Nelsovp Courses Elec22 Slides Interrupt Io part2 Pdf

List All Registers Which Will Be Saved In Stack Au Chegg Com

Interrupt Vector Table An Overview Sciencedirect Topics

Interrupt Vector Address In Program Counter Electrical Engineering Stack Exchange

Embedded Security 3 Immutable Boot Code Kickstart Embedded

Interrupt Vector Table An Overview Sciencedirect Topics

What Is Interrupt Vector Table In Arm Cortex M Microcontrollers

Debugging Hard Faults On Arm Cortex M Mcu On Eclipse

Manual Ports Armcm4 Tm4c Openblt Bootloader

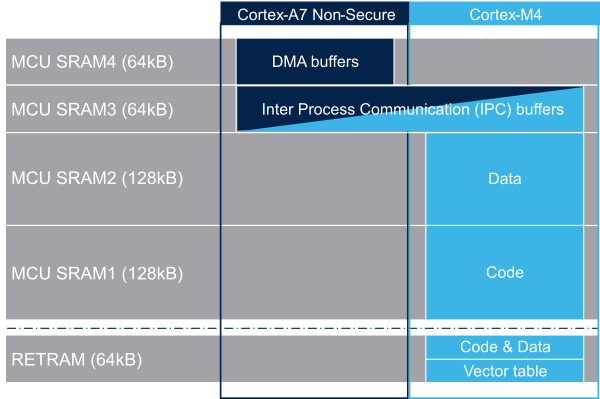

Stm32mp15 Ram Mapping Stm32mpu

6 2il Kvfjj Fm

Arm Cortex M Interrupts And Freertos Part 3 Mcu On Eclipse

Refer To Chapter 7 8 9 In The Reference Book Ppt Download

Analyzing Arm Cortex Based Mcu Firmwares Using Binary Ninja Kudelski Security Research

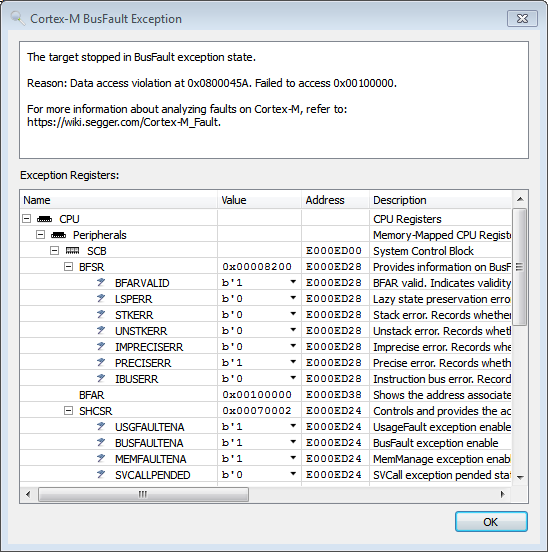

Cortex M Fault Segger Wiki

Www Eng Auburn Edu Nelsovp Courses Elec22 Slides Interrupt Io part2 Pdf